#### **FEATURES**

- Designed for Very Low-Power applications

- Offered in Tiny GREEN/RoHS compliant packages

- o 6-pin DFN (2.0mmx1.3mmx0.6mm)

- o 6-pin SC70 (2.3mmx2.25mmx1.0mm)

- o 6-pin SOT23 (3.0mmx3.0mmx1.35mm)

- Input Frequency:

- o Fundamental Crystal: 10MHz to 50MHz

- o Reference Input: 1MHz to 200MHz

- Accepts >0.1V reference signal input voltage

- Output Frequency:

- ≤65MHz @ 1.8V operation

- ≤90MHz @ 2.5V operation

- Disabled outputs programmable as HiZ or Active Low.

- Low current consumption:

- o <1.2mA @ 27MHz

- Single 1.8V, 2.5V, or 3.3V  $\pm$  10% power supply

- Operating temperature range from -40°C to 85°C

#### DESCRIPTION

The PL611s-28 consumes very low-power while producing high performance clock outputs of up to 55MHz. Designed for low-power applications with very stringent space requirement, PL611s-28 consumes about 1.2mA, while producing 2 distinct outputs of 27MHz and 13.5MHz. Designed to fit in a small SOT, SC70, or SOT23 package for high performance applications, the PL611s-28 offers excellent phase noise and jitter performance. The power down feature of PL611s-28, when activated, allows the IC to consume less than 5µA of power, while its programming flexibility allows generating any output, using a low-cost crystal or reference input. In addition, one programmable I/O pin can be configured as Output Enable (OE), Frequency switching (FSEL), Power Down (PDB) input, or CLK1 (FOUT, FREF, FREF/2) output.

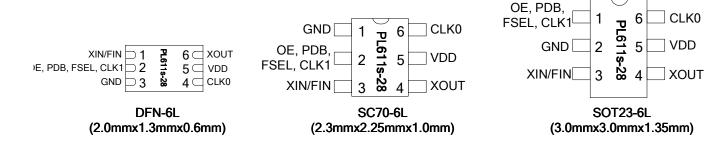

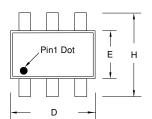

### PACKAGE PIN CONFIGURATION

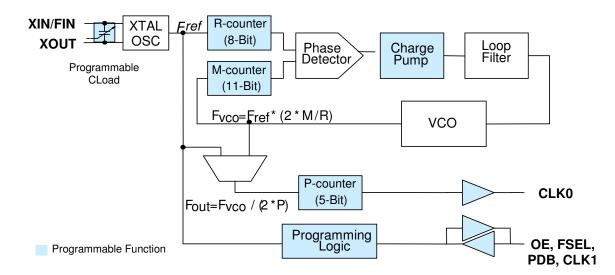

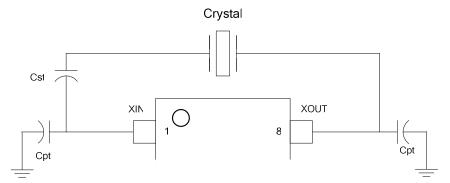

#### **BLOCK DIAGRAM**

# naseLink o r p o r a t i o n (Preliminary) PL611s-28 1.8V-3.3V PicoPLL<sup>TM</sup>, World's Smallest Programmable Clock

### **KEY PROGRAMMING PARAMETERS**

| CLK[0:1]<br>Output Frequency                                                          | Output Drive Strength                                                    | Programmable<br>Input/Output                                                                                        |

|---------------------------------------------------------------------------------------|--------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| FOUT = FREF * M / (R * P)  Where M = 11 bit  R = 8 bit                                | Three optional drive strengths to choose from:                           | One output pin can be configured as:                                                                                |

| P = 5 bit<br>CLK0 = Fout, Fref or Fref / (2*P)<br>CLK1 = Fref, Fref/2, CLK0 or CLK0/2 | <ul><li>Low: 4mA</li><li>Std: 8mA (default)</li><li>High: 16mA</li></ul> | <ul> <li>OE - input</li> <li>PDB - input</li> <li>FSEL - input</li> <li>HiZ or Active Low disabled state</li> </ul> |

### **PACKAGE PIN ASSIGNMENT**

|                        | Pin          | Assignn      | nent        |      |                                                                                                                                                                                                                                                                                                                                                                             |             |                 |               |  |

|------------------------|--------------|--------------|-------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------|---------------|--|

| Name                   | SOT<br>Pin # | SC70<br>Pin# | DFN<br>Pin# | Type | Description                                                                                                                                                                                                                                                                                                                                                                 |             |                 |               |  |

| OE, PDB,<br>FSEL, CLK1 | 1            | 2            | 2           | 1/0  | This programmable I/O pin can be configured as an Output Enable (OE) input, Power Down (PDB) input, On-the-Fly Frequency Switching Selector (FSEL)input or CLK1 clock output. This pin has an internal 60KΩ pull up resistor (OE, PDB & FSEL Only).  The OE and PDB features can be programmed to allow the output to float (Hi Z), or to operate in the 'Active low' mode. |             |                 |               |  |

|                        |              |              |             |      | State                                                                                                                                                                                                                                                                                                                                                                       | OE          | PDB             | FSEL          |  |

|                        |              |              |             |      | 0                                                                                                                                                                                                                                                                                                                                                                           | Disable CLK | Power Down Mode | Frequency '2' |  |

|                        |              |              |             |      | 1 (default) Normal mode Normal mode Frequency '1'                                                                                                                                                                                                                                                                                                                           |             |                 |               |  |

| GND                    | 2            | 1            | 3           | Р    | GND connection                                                                                                                                                                                                                                                                                                                                                              |             |                 |               |  |

| XIN, FIN               | 3            | 3            | 1           | I    | Crystal or Reference input pin                                                                                                                                                                                                                                                                                                                                              |             |                 |               |  |

| VOLIT                  | 4            | 4            |             | 0    | Crystal Output pin                                                                                                                                                                                                                                                                                                                                                          |             |                 |               |  |

| XOUT                   | 4            | 4            | 6           | 0    | Do Not Connect (DNC ) when FIN is present                                                                                                                                                                                                                                                                                                                                   |             |                 |               |  |

| VDD                    | 5            | 5            | 5           | Р    | VDD connection                                                                                                                                                                                                                                                                                                                                                              |             |                 |               |  |

| CLK0                   | 6            | 6            | 4           | 0    | Programmable Clock Output                                                                                                                                                                                                                                                                                                                                                   |             |                 |               |  |

#### **FUNCTIONAL DESCRIPTION**

PL611s-28 is a highly featured, very flexible, advanced programmable PLL design for high performance, low-power, small form-factor applications. The PL611s-28 accepts a fundamental input crystal of 10MHz to 50MHz or reference clock input of 1MHz to 200MHz and is capable of producing two outputs up to 125MHz. This flexible design allows the PL611s-28 to deliver any PLL generated frequency, FREF (Crystal or Ref Clk) frequency or FREF /(2\*P) to CLK0 and/or CLK1. Some of the design features of the PL611s-28 are mentioned below:

### **PLL Programming**

The PLL in the PL611s-28 is fully programmable. The PLL is equipped with an 8-bit input frequency divider (R-Counter), and an 11-bit VCO frequency feedback loop divider (M-Counter). The output of the PLL is transferred to a 5-bit post VCO divider (P-Counter). The output frequency is determined by the following formula [FOUT = FREF \* M / (R \* P)].

### **Clock Output (CLK0)**

CLK0 is the main clock output. The output of CLK0 can be configured as the PLL output ( $F_{VCO}/(2^*P)$ ), FREF (Crystal or Ref Clk Frequency) output, or FREF/( $2^*P$ ) output.

### **Clock Output (CLK1)**

The CLK1 feature allows the PL611s-28 to have an additional clock output. This output can be programmed to one of the following:

FREF - Reference (Crystal or Ref Clk) Frequency FREF / 2 CLK0 CLK0 / 2

The output drive level can be programmed to Low Drive (4mA), Standard Drive (8mA) or High Drive (16mA) for each clock independently. The maximum output frequency is 125MHz.

### Output Enable (OE)

The Output Enable feature allows the user to enable and disable the clock output(s) by toggling the OE pin. The OE pin incorporates a  $60k\Omega$  pull up resistor giving a default condition of logic "1".

The OE feature can be programmed to allow the output to float (Hi Z), or to operate in the 'Active low' mode.

### **Power-Down Control (PDB)**

The Power Down (PDB) feature allows the user to put the PL611s-28 into "Sleep Mode". When activated (logic '0'), PDB 'Disables the PLL, the oscillator circuitry, counters, and all other active circuitry. In Power Down mode the IC consumes <10 $\mu$ A of power. The PDB pin incorporates a 60k $\Omega$  pull up resistor giving a default condition of logic "1".

The PDB feature can be programmed to allow the output to float (Hi Z), or to operate in the 'Active low' mode.

### Frequency Select (FSEL)

The Frequency Select (FSEL) feature allows the PL611s-28 to switch between two pre-programmed outputs allowing the device "On the Fly" frequency switching. The FSEL pin incorporates a  $60k\Omega$  pull up resistor giving a default condition of logic "1".

# ELECTRICAL SPECIFICATIONS ABSOLUTE MAXIMUM RATINGS

| PARAMETERS                            | SYMBOL          | MIN. | MAX.                 | UNITS |

|---------------------------------------|-----------------|------|----------------------|-------|

| Supply Voltage Range                  | V <sub>DD</sub> | -0.5 | 7                    | V     |

| Input Voltage Range                   | Vı              | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Output Voltage Range                  | Vo              | -0.5 | V <sub>DD</sub> +0.5 | V     |

| Soldering Temperature (Green package) |                 |      | 260                  | °C    |

| Data Retention @ 85°C                 |                 | 10   |                      | Year  |

| Storage Temperature                   | Ts              | -65  | 150                  | °C    |

| Ambient Operating Temperature*        |                 | -40  | 85                   | °C    |

Exposure of the device under conditions beyond the limits specified by Maximum Ratings for extended periods may cause permanent damage to the device and affect product reliability. These conditions represent a stress rating only, and functional operations of the device at these or any other conditions above the operational limits noted in this specification is not implied. \*Operating temperature is guaranteed by design. Parts are tested to commercial grade only.

### **AC SPECIFICATIONS**

| PARAMETERS                                                | CONDITIONS                                                                  | MIN. | TYP. | MAX.     | UNITS |

|-----------------------------------------------------------|-----------------------------------------------------------------------------|------|------|----------|-------|

| Crystal Input Frequency (XIN)                             | Fundamental Crystal                                                         | 10   |      | 50       | MHz   |

|                                                           | @ V <sub>DD</sub> =3.3V                                                     |      |      | 200      |       |

| Input (FIN) Frequency                                     | @ V <sub>DD</sub> =2.5V                                                     |      |      | 166      | MHz   |

|                                                           | @ V <sub>DD</sub> =1.8V                                                     |      |      | 133      |       |

| Input (FIN) Signal Amplitude                              | Internally AC coupled (High Frequency)                                      | 0.9  |      | $V_{DD}$ | Vpp   |

| Input (FIN) Signal Amplitude                              | Internally AC coupled (Low Frequency) 3.3V <50MHz, 2.5V <40MHz, 1.8V <15MHz | 0.1  |      | $V_{DD}$ | Vpp   |

|                                                           | @ V <sub>DD</sub> =3.3V                                                     |      |      | 125      | MHz   |

| Output Frequency                                          | @ V <sub>DD</sub> =2.5V                                                     |      |      | 90       | MHz   |

|                                                           | @ V <sub>DD</sub> =1.8V                                                     |      |      | 65       | MHz   |

| Settling Time                                             | At power-up (after V <sub>DD</sub> increases over 1.62V)                    |      |      | 2        | ms    |

| Output Enable Time                                        | OE Function; Ta=25° C, 15pF Load                                            |      |      | 10       | ns    |

| Output Enable Time                                        | PDB Function; Ta=25° C, 15pF Load                                           |      |      | 2        | ms    |

| VDD Sensitivity                                           | Frequency vs. V <sub>DD</sub> +/-10%                                        | -2   |      | 2        | ppm   |

| Output Rise Time                                          | 15pF Load, 10/90% VDD, High Drive, 3.3V                                     |      | 1.2  | 1.7      | ns    |

| Output Fall Time                                          | 15pF Load, 90/10% VDD, High Drive, 3.3V                                     |      | 1.2  | 1.7      | ns    |

| Duty Cycle                                                | V <sub>DD</sub> /2                                                          | 45   | 50   | 55       | %     |

| Period Jitter,Pk-to-Pk*<br>(measured from 10,000 samples) | With capacitive decoupling between $V_{\text{DD}}$ and GND.                 |      | 70   |          | ps    |

<sup>\*</sup> Note: Jitter performance depends on the programming parameters.

### **DC SPECIFICATIONS**

| PARAMETERS                                                | SYMBOL           | CONDITIONS                                     | MIN.                  | TYP. | MAX. | UNITS |

|-----------------------------------------------------------|------------------|------------------------------------------------|-----------------------|------|------|-------|

| Supply Current, Dynamic, with Loaded CMOS Outputs         | I <sub>DD</sub>  | @ V <sub>DD</sub> =3.3V, 27MHz,<br>load=15pF   |                       | 4.0  |      | mA    |

| Supply Current, Dynamic, with Loaded CMOS Outputs         | $I_{DD}$         | @ V <sub>DD</sub> =2.5V, 27MHz,<br>load=10pF   |                       | 2.7  |      | mA    |

| Supply Current, Dynamic with Loaded CMOS Outputs          | $I_{DD}$         | @ V <sub>DD</sub> =1.8V, 27MHz,<br>load=5pF    |                       | 1.2  |      | mA    |

| PLL Off: Supply Current, Dynamic, with Loaded CMOS Output | I <sub>DD</sub>  | @ V <sub>DD</sub> =3.3V, 27MHz,<br>load=15pF   |                       | 2.0  |      | mA    |

| PLL Off: Supply Current, Dynamic, with Loaded CMOS Output | I <sub>DD</sub>  | @ V <sub>DD</sub> =2.5V, 27MHz,<br>load=10pF   |                       | 1.3  |      | mA    |

| PLL Off: Supply Current, Dynamic with Loaded CMOS Output  | I <sub>DD</sub>  | @ V <sub>DD</sub> =1.8V, 27MHz,<br>load=5pF    |                       | 0.8  |      | mA    |

| Supply Current, Dynamic, with Loaded Outputs              | $I_{DD}$         | When PDB=0                                     |                       |      | 5    | μA    |

| Operating Voltage                                         | $V_{DD}$         |                                                | 1.62                  |      | 3.63 | V     |

| Output Low Voltage                                        | Vol              | I <sub>OL</sub> = +4mA Standard Drive          |                       |      | 0.4  | V     |

| Output High Voltage                                       | V <sub>OH</sub>  | I <sub>OH</sub> = -4mA Standard Drive          | V <sub>DD</sub> - 0.4 |      |      | V     |

| Output Current, Low Drive                                 | I <sub>OSD</sub> | V <sub>OL</sub> = 0.4V, V <sub>OH</sub> = 2.4V | 4                     |      |      | mA    |

| Output Current, Standard Drive                            | Iosp             | V <sub>OL</sub> = 0.4V, V <sub>OH</sub> = 2.4V | 8                     |      |      | mA    |

| Output Current, High Drive                                | I <sub>OHD</sub> | V <sub>OL</sub> = 0.4V, V <sub>OH</sub> = 2.4V | 16                    |      |      | mA    |

<sup>\*</sup> Note: Please contact PhaseLink, if super-low-power is required.

### **CRYSTAL SPECIFICATIONS**

| PAF                                                                            | SYMBOL            | MIN.                  | TYP. | MAX. | UNITS |     |

|--------------------------------------------------------------------------------|-------------------|-----------------------|------|------|-------|-----|

| Fundamental Crystal Res                                                        | sonator Frequency | Fxin                  | 10   |      | 50    | MHz |

| Crystal Loading Rating (The IC can be programmed for any value in this range.) |                   | C <sub>L</sub> (xtal) | 8    |      | 12    | pF  |

| Maximum Sustainable Drive Level                                                |                   |                       |      |      | 100   | μW  |

| Operating Drive Level                                                          |                   |                       |      | 30   |       | μW  |

| Matal Can Cryatal                                                              | Shunt Capacitance | C0                    |      |      | 5.5   | pF  |

| Metal Can Crystal                                                              | ESR Max           | ESR                   |      |      | 50    | Ω   |

| Consult CMD Consultati                                                         | Shunt Capacitance | C0                    |      |      | 2.5   | pF  |

| Small SMD Crystal                                                              | ESR Max           | ESR                   |      |      | 80    | Ω   |

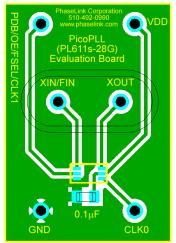

### LAYOUT RECOMMENDATIONS

**DFN-6L Evaluation Board**

The following guidelines are to assist you with a performance optimized PCB design:

# Signal Integrity and Termination Considerations

- Keep traces short!

- Trace = Inductor. With a capacitive load this equals ringing!

- Long trace = Transmission Line. Without proper termination this will cause reflections ( looks like ringing ).

- Design long traces as "striplines" or "microstrips" with defined impedance.

- Match trace at one side to avoid reflections bouncing back and forth.

# **Decoupling and Power Supply Considerations**

- Place decoupling capacitors as close as possible to the VDD pin(s) to limit noise from the power supply

- Multiple VDD pins should be decoupled separately for best performance.

- Addition of a ferrite bead in series with VDD can help prevent noise from other board sources

- Value of decoupling capacitor is frequency dependant. Typical values to use are  $0.1\mu F$  for designs using crystals < 50MHz and  $0.01\mu F$  for designs using crystals > 50MHz.

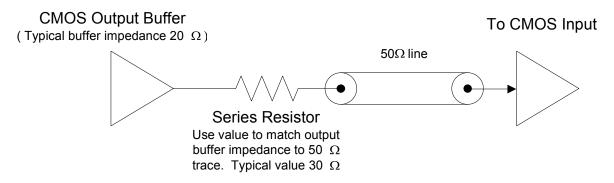

### **Typical CMOS termination**

Place Series Resistor as close as possible to CMOS output

### **Crystal Tuning Circuit**

Series and parallel capacitors used to fine tune the crystal load to the circuit load.

CST - Series Capacitor, used to lower circuit load to match crystal load. Raises frequency offset. This can be eliminated by using a crystal with a Cload of equal or greater value than the oscillator.

**CPT** - Parallel Capacitors, Used to raise the circuit load to match the crystal load. Lowers frequency offset.

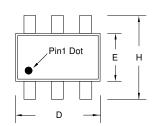

### PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

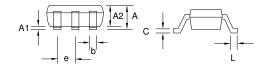

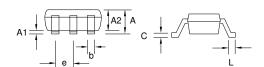

### **SOT23-6L**

| Symbol | Dimension in MM |      |  |

|--------|-----------------|------|--|

| Symbol | Min.            | Max. |  |

| Α      | 1.05            | 1.35 |  |

| A1     | 0.05            | 0.15 |  |

| A2     | 1.00            | 1.20 |  |

| b      | 0.30            | 0.50 |  |

| С      | 0.08            | 0.20 |  |

| D      | 2.80            | 3.00 |  |

| Е      | 1.50            | 1.70 |  |

| Н      | 2.60            | 3.00 |  |

| L      | 0.35            | 0.55 |  |

| е      | 0.95 BSC        |      |  |

### SC70-6L

| Symbol   | Dimension in MM |      |  |  |

|----------|-----------------|------|--|--|

| Syllibol | Min.            | Max. |  |  |

| Α        | 0.80            | 1.00 |  |  |

| A1       | 0.00            | 0.09 |  |  |

| A2       | 0.80            | 0.91 |  |  |

| b        | 0.15            | 0.30 |  |  |

| С        | 0.08            | 0.25 |  |  |

| D        | 1.85            | 2.25 |  |  |

| E        | 1.15            | 1.35 |  |  |

| Н        | 2.00            | 2.30 |  |  |

| Ĺ        | 0.21            | 0.41 |  |  |

| е        | 0.65BSC         |      |  |  |

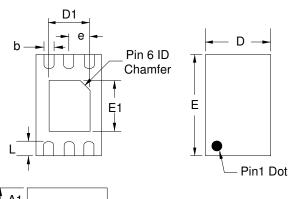

### DFN-6L

| Symbol   | Dimension in MM |       |  |  |

|----------|-----------------|-------|--|--|

| Syllibol | Min.            | Max.  |  |  |

| Α        | 0.50            | 0.60  |  |  |

| A1       | 0.00            | 0.05  |  |  |

| A3       | 0.152           | 0.152 |  |  |

| b        | 0.15            | 0.25  |  |  |

| е        | 0.40BSC         |       |  |  |

| D        | 1.25            | 1.35  |  |  |

| E        | 1.95            | 2.05  |  |  |

| D1       | 0.75            | 0.85  |  |  |

| E1       | 0.95            | 1.05  |  |  |

| Ĺ        | 0.20            | 0.30  |  |  |

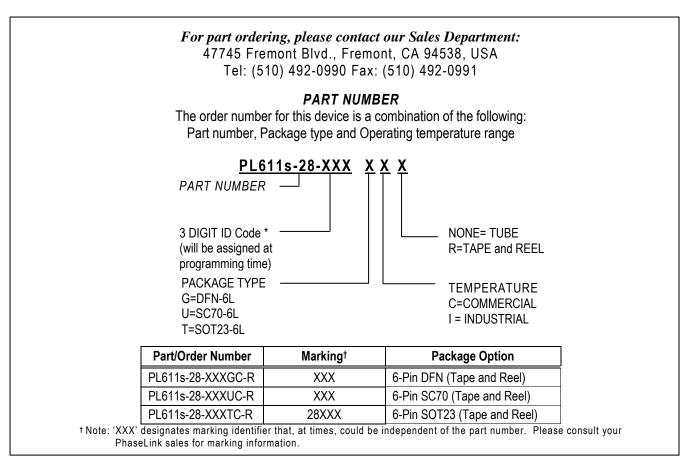

### ORDERING INFORMATION (GREEN PACKAGE)

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Phaselink is believed to be accurate and reliable. However, PhaseLink makes no guarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: PhaseLink's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.

Solder reflow profile available at www.phaselink.com/QA/solderingGreen.pdf